Une nouvelle conception de puces coupe la consommation d'énergie de l'IA en permettant un traitement FPGA plus intelligent

Une nouvelle innovation des chercheurs de Cornell réduit la consommation d'énergie nécessaire pour alimenter l'intelligence artificielle – une étape vers la réduction des empreintes carbone des centres de données et des infrastructures d'IA.

À mesure que les systèmes d'IA deviennent de plus en plus puissants, ils deviennent également plus avides de pouvoir – sur les questions urgentes sur la durabilité. L'équipe de recherche, de Cornell Tech et Cornell Engineering, relève ce défi en repensant le matériel qui alimente l'IA, visant à le rendre plus rapide, plus efficace et moins intensif.

Les chercheurs ont reçu un prix du meilleur article pour leurs résultats, présenté à la Conférence internationale sur la logique et les applications programmables sur le terrain (FPL 2025), du 1er au 5 septembre à Leiden, aux Pays-Bas. Le papier est disponible sur le arxiv serveur de préimprimée.

Leur travail se concentre sur un type de puce d'ordinateur appelée un tableau de porte programmable sur le terrain (FPGA). Ces puces sont appréciées pour leur flexibilité: contrairement aux puces traditionnelles, elles peuvent être reprogrammées pour différentes tâches après la fabrication. Cela les rend particulièrement utiles dans des champs en évolution rapide tels que l'IA, le cloud computing et la communication sans fil.

« Les FPGA sont partout – des cartes réseau et des stations de base de communication aux machines à ultrasons, aux analyses de chats et même aux machines à laver », a déclaré le co-auteur Mohamed Abdelfattah, professeur adjoint chez Cornell Tech. « L'IA arrive à tous ces appareils, et cette architecture aide à rendre cette transition plus efficace, »

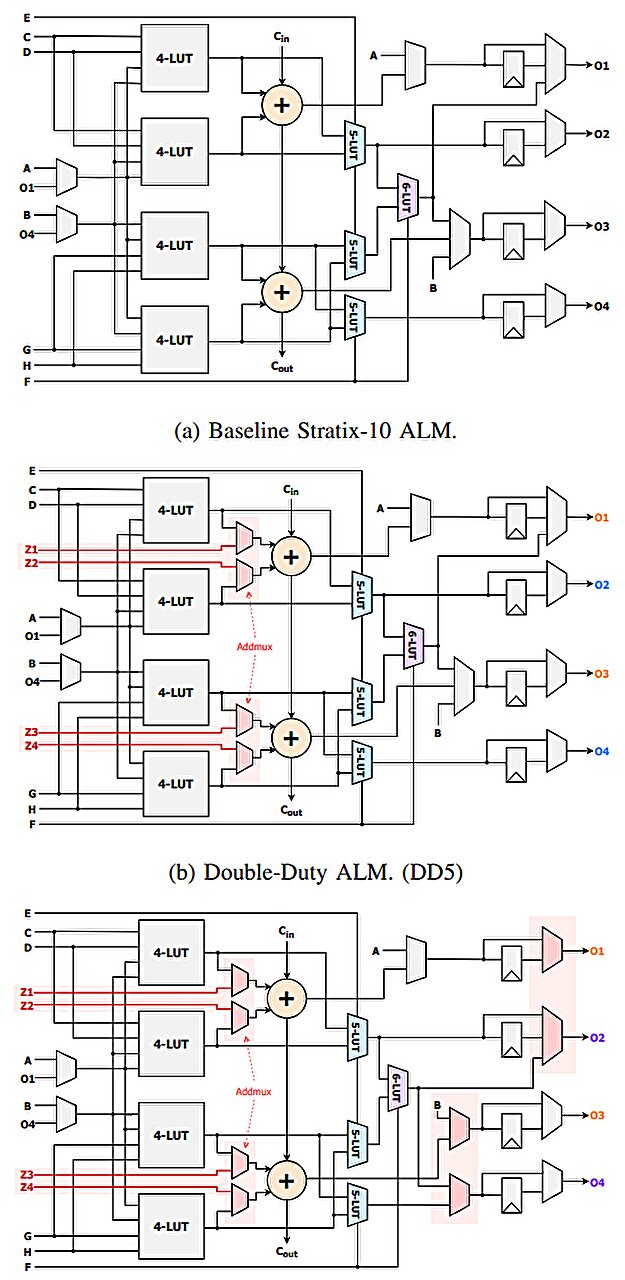

À l'intérieur de chaque puce FPGA se trouvent des unités de calcul appelées blocs logiques. Ces blocs contiennent des composants qui peuvent gérer différents types de calcul. Les tables de recherche (LUTS) sont des composants qui peuvent effectuer une large gamme d'opérations logiques en fonction de ce que la puce doit faire. Les chaînes additionnelles sont des composants qui effectuent des opérations arithmétiques rapides telles que l'ajout de nombres – essentiels pour des tâches telles que la reconnaissance d'image et le traitement du langage naturel.

Dans les conceptions FPGA conventionnelles, ces composants sont étroitement liés, ce qui signifie que les chaînes d'additionces ne sont accessibles que via les LUTS. Cela limite l'efficacité de la puce, en particulier pour les charges de travail de l'IA qui reposent fortement sur les opérations arithmétiques.

L'équipe de recherche a développé « Double Duty », une nouvelle architecture de puces, pour résoudre ce problème. La conception permet aux LUTS et aux chaînes d'additionces de fonctionner de manière indépendante et simultanément dans le même bloc logique. En d'autres termes, la puce peut désormais faire plus avec les mêmes ressources de traitement exactes.

Cette innovation a particulièrement un impact pour les réseaux de neurones profonds, des modèles d'IA qui imitent le traitement des informations du cerveau humain. Ces modèles sont souvent «déroulés» sur les FPGA – déposés en circuits fixes pour un traitement plus rapide et plus efficace.

« Nous nous sommes concentrés sur un mode où les FPGA sont en fait vraiment bons dans l'accélération de l'IA », a déclaré Abdelfattah, qui est également affilié à Cornell Engineering. « En réalisant un petit changement architectural, nous rendons ces réseaux de neurones déroulés beaucoup plus efficaces, jouant avec les forces des FPGA au lieu de les traiter comme des processeurs génériques. »

Lors des tests, la conception à double service a réduit l'espace nécessaire pour des tâches AI spécifiques de plus de 20% et amélioré les performances globales sur une grande suite de circuits de près de 10%. Cela signifie que moins de puces pourraient être utilisées pour effectuer le même travail, ce qui entraîne une consommation d'énergie plus faible.

L'impact va au-delà de l'IA. « Ce changement profite également aux industries traditionnelles », a déclaré Xilai Dai, doctorant en génie électrique et informatique et l'un des principaux auteurs du journal. « Il aide à la vérification des puces, à la communication sans fil et à toute application qui utilise l'arithmétique. Vous pouvez intégrer des programmes plus importants dans des puces plus petites, ce qui améliore l'efficacité à tous les niveaux. »

Les travaux ont commencé comme un projet de recherche de premier cycle par Dai, qui a continué à développer l'idée en une étude à grande échelle lors de ses études à Cornell. L'autre co-auteur principal du journal, Junius Pun, ancien stagiaire de recherche chez Cornell Tech et diplômé récent de la Nanyang Technological University, a également joué un rôle clé dans le travail d'architecture et de modélisation.

Le projet comprenait également des chercheurs de l'Université de Toronto et de l'Université de Waterloo, ainsi que des ingénieurs d'Altera (anciennement partie d'Intel).

« Ce fut une grande collaboration entre les partenaires universitaires et l'industrie, avec de nombreuses pièces émouvantes », a déclaré Abdelfattah. « C'est une étape vers l'utilisation des FPGA d'une manière qui joue à leurs forces, ce qui les rend vraiment efficaces. »